## TLC5615 10-BIT DIGITAL-TO-ANALOG CONVERTERS

- 10-Bit CMOS Voltage Output DAC in an 8-Terminal Package

- 5-V Single Supply Operation

- 3-Wire Serial Interface

- High-Impedance Reference Inputs

- Voltage Output Range . . . 2 Times the Reference Input Voltage

- Internal Power-On Reset

- Low Power Consumption . . . 1.75 mW Max

- Update Rate of 1.21 MHz

- Settling Time to 0.5 LSB . . . 12.5 μs Typ

- Monotonic Over Temperature

- Pin Compatible With the Maxim MAX515

#### applications

- Battery-Powered Test Instruments

- Digital Offset and Gain Adjustment

- Battery Operated/Remote Industrial Controls

- Machine and Motion Control Devices

- Cellular Telephones

#### description

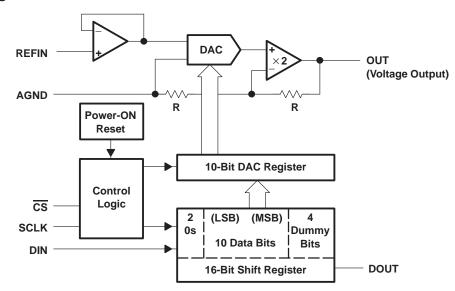

The TLC5615 is a 10-bit voltage output digital-to-analog converter (DAC) with a buffered reference input (high impedance). The DAC has an output voltage range that is two times the reference voltage, and the DAC is monotonic. The device is simple to use, running from a single supply of 5 V. A power-on-reset function is incorporated to ensure repeatable start-up conditions.

Digital control of the TLC5615 is over a three-wire serial bus that is CMOS compatible and easily interfaced to industry standard microprocessor and microcontroller devices. The device receives a 16-bit data word to produce the analog output. The digital inputs feature Schmitt triggers for high noise immunity. Digital communication protocols include the SPI™, QSPI™, and Microwire™ standards.

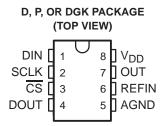

The 8-terminal small-outline D package allows digital control of analog functions in space-critical applications. The TLC5615C is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. The TLC5615I is characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C.

## functional block diagram

#### **Terminal Functions**

| TERMIN   | NAL | 1/0 | DESCRIPTION                           |

|----------|-----|-----|---------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                           |

| DIN      | 1   | I   | Serial data input                     |

| SCLK     | 2   | I   | Serial clock input                    |

| CS       | 3   | I   | Chip select, active low               |

| DOUT     | 4   | 0   | Serial data output for daisy chaining |

| AGND     | 5   |     | Analog ground                         |

| REFIN    | 6   | ı   | Reference input                       |

| OUT      | 7   | 0   | DAC analog voltage output             |

| $V_{DD}$ | 8   |     | Positive power supply                 |

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage (V <sub>DD</sub> to AGND)                        |                                                                                                                      |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Digital input voltage range to AGND                             |                                                                                                                      |

| Reference input voltage range to AGND                           | $\dots \dots $ |

| Output voltage at OUT from external source                      | V <sub>DD</sub> + 0.3 V                                                                                              |

| Continuous current at any terminal                              | $\dots \dots \pm 20 \text{ mA}$                                                                                      |

| Operating free-air temperature range, T <sub>A</sub> : TLC5615C | 0°C to 70°C                                                                                                          |

| TLC5615I                                                        | 40°C to 85°C                                                                                                         |

| Storage temperature range, T <sub>stq</sub>                     | 65°C to 150°C                                                                                                        |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds    | 260°C                                                                                                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                                                       |          | MIN | NOM   | MAX                | UNIT |

|-------------------------------------------------------|----------|-----|-------|--------------------|------|

| Supply voltage, V <sub>DD</sub>                       |          | 4.5 | 5     | 5.5                | V    |

| High-level digital input voltage, VIH                 |          | 2.4 |       |                    | V    |

| Low-level digital input voltage, V <sub>IL</sub>      |          |     |       | 8.0                | V    |

| Reference voltage, V <sub>ref</sub> to REFIN terminal |          | 2   | 2.048 | V <sub>DD</sub> -2 | V    |

| Load resistance, R <sub>L</sub>                       |          | 2   |       |                    | kΩ   |

| Operating free air temperature. Te                    | TLC5615C | 0   |       | 70                 | °C   |

| Operating free-air temperature, T <sub>A</sub>        | TLC5615I | -40 |       | 85                 | °C   |

# electrical characteristics over recommended operating free-air temperature range, $V_{DD} = 5 \text{ V} \pm 5\%$ , $V_{ref} = 2.048 \text{ V} \text{ (unless otherwise noted)}$

#### static DAC specifications

|      | PARAMETER                                |            | TEST CON                | DITIONS    | MIN | TYP                          | MAX   | UNIT   |

|------|------------------------------------------|------------|-------------------------|------------|-----|------------------------------|-------|--------|

|      | Resolution                               |            |                         |            | 10  |                              |       | bits   |

|      | Integral nonlinearity, end point adjuste | ed (INL)   | $V_{ref} = 2.048 V$ ,   | See Note 1 |     |                              | ±1    | LSB    |

|      | Differential nonlinearity (DNL)          |            | $V_{ref} = 2.048 V$ ,   | See Note 2 |     | ±0.1                         | ± 0.5 | LSB    |

| EZS  | Zero-scale error (offset error at zero s | cale)      | $V_{ref} = 2.048 V$ ,   | See Note 3 |     |                              | ±3    | LSB    |

|      | Zero-scale-error temperature coefficie   | ent        | $V_{ref} = 2.048 V$ ,   | See Note 4 |     | 3                            |       | ppm/°C |

| EG   | Gain error                               |            | $V_{ref} = 2.048 V$ ,   | See Note 5 |     |                              | ±3    | LSB    |

|      | Gain-error temperature coefficient       |            | $V_{ref} = 2.048 V$ ,   | See Note 6 |     | 1                            |       | ppm/°C |

| DCDD | Davis a comple sais ation satis          | Zero scale | Con Notes 7 and         | 0          | 80  |                              |       | 40     |

| PSRR | Power-supply rejection ratio             | Gain       | See Notes 7 and 8       |            | 80  |                              |       | dB     |

|      | Analog full scale output                 |            | R <sub>L</sub> = 100 kΩ |            | 2\  | / <sub>ref</sub> (1023/1024) |       | V      |

#### NOTES: 1. The relative accuracy or integral nonlinearity (INL), sometimes referred to as linearity error, is the maximum deviation of the output from the line between zero and full scale excluding the effects of zero code and full-scale errors (see text).

- 2. The differential nonlinearity (DNL), sometimes referred to as differential error, is the difference between the measured and ideal 1 LSB amplitude change of any two adjacent codes. Monotonic means the output voltage changes in the same direction (or remains constant) as a change in the digital input code.

- 3. Zero-scale error is the deviation from zero-voltage output when the digital input code is zero (see text).

- 4. Zero-scale-error temperature coefficient is given by:  $E_{ZS}TC = [E_{ZS}(T_{max}) E_{ZS}(T_{min})]/V_{ref} \times 10^6/(T_{max} T_{min})$ .

- 5. Gain error is the deviation from the ideal output ( $V_{ref}$  1 LSB) with an output load of 10 k $\Omega$  excluding the effects of the zero-scale

- 6. Gain temperature coefficient is given by:  $E_G TC = [E_G(T_{max}) E_G(T_{min})]/V_{ref} \times 10^6/(T_{max} T_{min})$ . 7. Zero-scale-error rejection ratio (EZS-RR) is measured by varying the  $V_{DD}$  from 4.5 V to 5.5 V dc and measuring the proportion of this signal imposed on the zero-code output voltage.

- 8. Gain-error rejection ratio (EG-RR) is measured by varying the V<sub>DD</sub> from 4.5 V to 5.5 V dc and measuring the proportion of this signal imposed on the full-scale output voltage after subtracting the zero-scale change.

#### voltage output (OUT)

|                      | PARAMETER                       | TEST CONDITIONS                                            | MIN  | TYP | MAX                  | UNIT |

|----------------------|---------------------------------|------------------------------------------------------------|------|-----|----------------------|------|

| VO                   | Voltage output range            | $R_L = 10 \text{ k}\Omega$                                 | 0    |     | V <sub>DD</sub> -0.4 | V    |

|                      | Output load regulation accuracy | $V_{O(OUT)} = 2 \text{ V}, \qquad R_L = 2 \text{ k}\Omega$ |      |     | 0.5                  | LSB  |

| losc                 | Output short circuit current    | OUT to V <sub>DD</sub> or AGND                             |      | 20  |                      | mA   |

| V <sub>OL(low)</sub> | Output voltage, low-level       | $I_{O(OUT)} \le 5 \text{ mA}$                              |      |     | 0.25                 | V    |

| VOH(high)            | Output voltage, high-level      | I <sub>O(OUT)</sub> ≤ −5 mA                                | 4.75 |     |                      | V    |

electrical characteristics over recommended operating free-air temperature range,  $V_{DD}$  = 5 V  $\pm$  5%,  $V_{ref}$  = 2.048 V (unless otherwise noted) (continued)

# reference input (REFIN)

|                | PARAMETER         | TEST CONDITIONS | MIN | TYP | MAX                | UNIT |

|----------------|-------------------|-----------------|-----|-----|--------------------|------|

| ٧ <sub>I</sub> | Input voltage     |                 | 0   |     | V <sub>DD</sub> -2 | V    |

| rį             | Input resistance  |                 | 10  |     |                    | MΩ   |

| Ci             | Input capacitance |                 |     | 5   |                    | pF   |

# digital inputs (DIN, SCLK, CS)

|     | PARAMETER                        | TEST CONDITIONS    | MIN | TYP | MAX | UNIT |

|-----|----------------------------------|--------------------|-----|-----|-----|------|

| VIH | High-level digital input voltage |                    | 2.4 |     |     | V    |

| VIL | Low-level digital input voltage  |                    |     |     | 0.8 | V    |

| lн  | High-level digital input current | $V_I = V_{DD}$     |     |     | ±1  | μΑ   |

| IJЦ | Low-level digital input current  | V <sub>I</sub> = 0 |     |     | ±1  | μΑ   |

| Ci  | Input capacitance                |                    |     | 8   |     | pF   |

## digital output (DOUT)

|     | PARAMETER                  | TEST CONDITIONS       | MIN                | TYP | MAX | UNIT |

|-----|----------------------------|-----------------------|--------------------|-----|-----|------|

| Vон | Output voltage, high-level | $I_O = -2 \text{ mA}$ | V <sub>DD</sub> -1 |     |     | V    |

| VOL | Output voltage, low-level  | $I_O = 2 \text{ mA}$  |                    |     | 0.4 | V    |

#### power supply

|          | PARAMETER            | TEST CONDI                                                      | TIONS                      | MIN | TYP | MAX | UNIT |

|----------|----------------------|-----------------------------------------------------------------|----------------------------|-----|-----|-----|------|

| $V_{DD}$ | Supply voltage       |                                                                 |                            | 4.5 | 5   | 5.5 | V    |

|          | Dougs cumply current | $V_{DD} = 5.5 \text{ V},$ No load, All inputs = 0 V or $V_{DD}$ | V <sub>ref</sub> = 0       |     | 150 | 250 | μΑ   |

| DD       | Power supply current | $V_{DD} = 5.5 \text{ V},$ No load, All inputs = 0 V or $V_{DD}$ | V <sub>ref</sub> = 2.048 V |     | 230 | 350 | μΑ   |

# analog output dynamic performance

| PARAMETER                             | TEST CONDITIONS                                                                                  | MIN | TYP | MAX | UNIT |

|---------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Signal-to-noise + distortion, S/(N+D) | V <sub>ref</sub> = 1 V <sub>pp</sub> at 1 kHz + 2.048 Vdc,<br>code = 11 1111 1111,<br>See Note 9 | 60  |     |     | dB   |

NOTE 9: The limiting frequency value at 1 Vpp is determined by the output-amplifier slew rate.

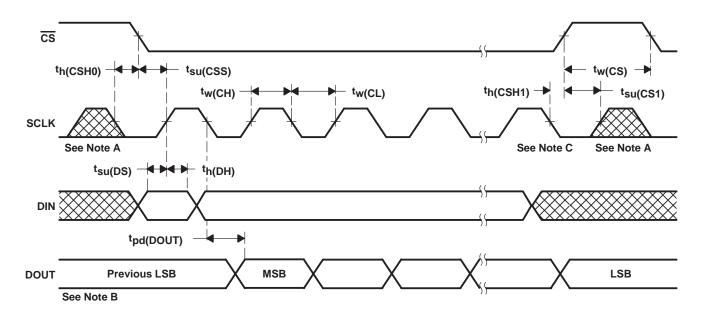

# digital input timing requirements (see Figure 1)

|                      | PARAMETER                                            | MIN | NOM | MAX | UNIT |

|----------------------|------------------------------------------------------|-----|-----|-----|------|

| t <sub>su(DS)</sub>  | Setup time, DIN before SCLK high                     | 45  |     |     | ns   |

| th(DH)               | Hold time, DIN valid after SCLK high                 | 0   |     |     | ns   |

| t <sub>su(CSS)</sub> | Setup time, CS low to SCLK high                      | 1   |     |     | ns   |

| t <sub>su(CS1)</sub> | Setup time, CS high to SCLK high                     | 50  |     |     | ns   |

| th(CSH0)             | Hold time, SCLK low to CS low                        | 1   |     |     | ns   |

| th(CSH1)             | Hold time, SCLK low to CS high                       | 0   |     |     | ns   |

| tw(CS)               | Pulse duration, minimum chip select pulse width high | 20  |     |     | ns   |

| tw(CL)               | Pulse duration, SCLK low                             | 25  |     |     | ns   |

| tw(CH)               | Pulse duration, SCLK high                            | 25  |     |     | ns   |

# output switching characteristic

| PARAMETER                                          | TEST CONDITIONS       | MIN | NOM | MAX | UNIT |

|----------------------------------------------------|-----------------------|-----|-----|-----|------|

| t <sub>pd(DOUT)</sub> Propagation delay time, DOUT | $C_L = 50 \text{ pF}$ |     |     | 50  | ns   |

# operating characteristics over recommended operating free-air temperature range, $V_{DD}$ = 5 V $\pm$ 5%, $V_{ref}$ = 2.048 V (unless otherwise noted)

## analog output dynamic performance

| PARAMETER      |                      | TEST CONDITIONS                                                                | MIN | TYP  | MAX | UNIT |

|----------------|----------------------|--------------------------------------------------------------------------------|-----|------|-----|------|

| SR             | Output slew rate     | $C_L = 100 \text{ pF},$ $R_L = 10 \text{ k}\Omega,$ $T_A = 25^{\circ}\text{C}$ | 0.3 | 0.5  |     | V/μs |

| t <sub>S</sub> | Output settling time | To 0.5 LSB, $C_L = 100$ pF, $R_L = 10$ kΩ, See Note 10                         |     | 12.5 |     | μs   |

|                | Glitch energy        | DIN = All 0s to all 1s                                                         |     | 5    |     | nV∙s |

NOTE 10: Settling time is the time for the output signal to remain within  $\pm 0.5$  LSB of the final measured value for a digital input code change of 000 hex to 3FF hex or 3FF hex to 000 hex.

## reference input (REFIN)

| PARAMETER                            | TEST CONDITIONS                                              |                                         |     | TYP | MAX | UNIT |

|--------------------------------------|--------------------------------------------------------------|-----------------------------------------|-----|-----|-----|------|

| Reference feedthrough                | REFIN = 1 V <sub>pp</sub> at 1 kHz + 2.048 Vdc (see Note 11) |                                         | -80 |     |     | dB   |

| Reference input<br>bandwidth (f–3dB) | REFIN = 0.2 V <sub>pp</sub> + 2.048 Vdc                      | REFIN = 0.2 V <sub>pp</sub> + 2.048 Vdc |     | 30  | ·   | kHz  |

NOTE 11: Reference feedthrough is measured at the DAC output with an input code = 000 hex and a  $V_{ref}$  input = 2.048 Vdc + 1  $V_{pp}$  at 1 kHz.

## PARAMETER MEASUREMENT INFORMATION

NOTES: A. The input clock, applied at the SCLK terminal, should be inhibited low when  $\overline{\text{CS}}$  is high to minimize clock feedthrough.

- B. Data input from preceeding conversion cycle.

- C. Sixteenth SCLK falling edge